- Synchronous refers to something that is time-synchronized with others. Synchronous signals occur at the same clock rate, and all clocks follow the same reference clock.

- We saw in the previous tutorial on Asynchronous Counter that the output of that counter is directly connected to the input of the next subsequent counter, forming a chain system, and that as a result of this chain system propagation delay appears during the counting stage, causing counting delays. The clock input across all flip-flops in a synchronous counter uses the same source and generates the same clock signal at the same time. A Synchronous counter uses the same clock signal from the same source at the same time.

Synchronous Counter Design and Operation

- The synchronous counter’s design and operation are described below. The circuit diagram for the 3-bit synchronous counter is shown below, and it is designed with two AND logic gates, three J-K FFs, and a CLK signal to enable the Flip Flop.

- An active high signal is applied to the input terminal of flip flop A in this example. As a result, it toggles at the reducing edge of each CLK input. Similarly, an AND gate is provided to the flip flop -B, whose output is primarily determined by the previous FF’s input and output B in this case. When the AND gate is turned on, flip-flop B will simply toggle when the flip-flop A output is high.

- In this case, the flip-flop C input will be the output of the second AND gate. When the A2 logic gate is activated, flip-flop C simply toggles. When the A1 logic gate and Flip Flop-B outputs are both high, the A2 logic gate is activated.

- Let’s look at how a 3-bit synchronous counter works. When the flip-flops are set to zero at the start of the circuit, the outputs of the three flip-flops will be zero, as in QCQBQA = 000. However, when the primary CLK signal drops, the flip-flop A output toggles from zero to one. So there will be no change at flip-flops B and FF-C because their input terminals are zero until the next CLK signal arrives.

- As a result, when the first CLK signal is applied, the flip-flop outputs will be QCQBQA = 001. Due to the high gate A1 output, both FFs such as A and B inputs will be 1 before applying the second clock signal. As a result, at the dropping edge of the second CLK signal, both Flip Flops will toggle again. As a result, the FFA output will be changed from one to zero, and the FFB output will be changed from zero to one. As a result, the output will be 010, and both logic gates A1 and A2 will be turned off.

- When the third clock signal is applied, the flip-flop-A output toggles and logic gates A1 & A1 turn ON, resulting in an output of 011. When the fourth clock signal is applied, all three FFs inputs in the circuit will be high. As a result, the dropping edge of the fourth flip-flop toggles all of the flip-flop outputs, changing QA & QB to 0 and QC to 1. As a result, the overall o/p of this CLK signal will be 100, and logic gates A1 and A2 will be turned off.

- When the next CLK signal appears, the FF-A output will again toggle from low to high at the dropping edge of the fifth CLK signal. As a result, the outputs QCQBQA will total 10, activating logic gates A1 and A2.

- When the sixth CLK signal is applied, flip-flop A toggles from 1 to 0 at its dropping edge. Also, because the input to flip-flop B is high, its output toggles from 0 to 1. As a result, QCQBQA will be 110 in this case. This process will continue, and at the dropping edge of the 8th CLK signal, all FFs outputs such as QCQBQA will be reset to 000.

- When the sixth CLK signal is applied, flip-flop A toggles from 1 to 0 at its dropping edge. Also, because the input to flip-flop B is high, its output toggles from 0 to 1. As a result, QCQBQA will be 110 in this case. This process will continue, and at the dropping edge of the 8th CLK signal, all FFs outputs such as QCQBQA will be reset to 000.

1. 4-bit Synchronous Up Counter

- A 4-bit up counter can be designed in the same way as a 3-bit synchronous up counter, but with four flip-flops. The diagram below depicts this. This counter has 16 output states and can count from 0000 to 1111.

- This counter can count in two ways: up counting and down counting. There is a mode switch that toggles between the counter’s two modes. When mode M is 0, it counts up, and when mode M is 1, it counts down.

- The 4-bit synchronous up counter timing diagram is shown below.

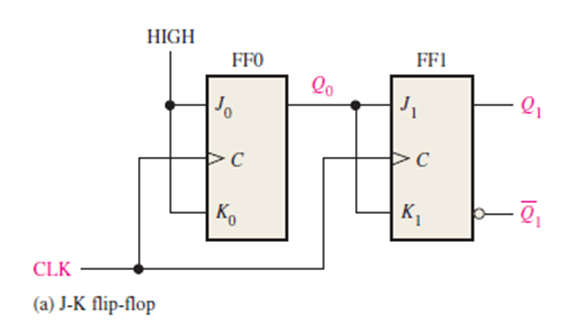

- The external clock pulses (to be counted) are fed directly to each of the J-K flip-flops in the counter chain, and both the J and K inputs are all tied together in toggle mode, but only the first flip-flop, flip-flop FFA (LSB), is connected HIGH, logic “1,” allowing the flip-flop to toggle on every clock pulse. The synchronous counter then advances one state for each pulse in response to the common clock signal, following a predetermined sequence of states.

- The J and K inputs of flip-flop FFB are directly connected to the output QA of flip-flop FFA, whereas the J and K inputs of flip-flops FFC and FFD are driven by separate AND gates that are also supplied with signals from the previous stage’s input and output. These additional AND gates generate the logic required for the next stage’s JK inputs.

- We can get the same counting sequence as with the asynchronous circuit but without the ripple effect if we enable each JK flip-flop to toggle based on whether or not all preceding flip-flop outputs (Q) are “HIGH.”

- The maximum operating frequency of this type of frequency counter is much higher than that of a similar asynchronous counter circuit because there is no inherent propagation delay in synchronous counters because all counter stages are triggered in parallel at the same time.

2. 4-bit Synchronous Down Counter

- This counter’s primary function is to count the numbers in decreasing order. The down counter is the same as the up counter, but it must reduce its count. Thus, the JK flip-flop inputs are connected to the Q’, and the same external CLK signal is connected to the circuit’s four flip-flops.

- Because this 4-bit synchronous counter counts sequentially on each clock pulse, the outputs range from 0 (0000) to 15. ( 1111 ). As a result, this counter is also known as a 4-bit Synchronous Up Counter.

- However, we can easily build a 4-bit Synchronous Down Counter by connecting the AND gates to the Q output of the flip-flops as shown to produce the opposite waveform timing diagram. In this case, the counter begins with all of its outputs HIGH (1111) and counts down on the application of each clock pulse to zero, (0000), before repeating.

- Because synchronous counters are built by connecting flip-flops, and any number of flip-flops can be connected or “cascaded” together to form a “divide-by-n” binary counter, the modulo’s or “MOD” number still applies, allowing a Decade counter or BCD counter with counts ranging from 0 to 2n-1 to be built alongside truncated sequences. To increase the MOD count of an up or down synchronous counter, we simply add another flip-flop and AND gate across it.

3. Decade 4-bit Synchronous Counter

- A decade counter counts ten different states before returning to its initial values. A simple decade counter counts from 0 to 9, but we can also create decade counters that can cycle through any ten states from 0 to 15. (for 4-bit counter).

- Edge-triggered flip-flops on the control input change states on either the “positive-edge” (rising edge) or the “negative-edge” (falling edge) of the clock pulse, resulting in a single count when the clock input changes state.

- In general, synchronous counters count on the rising edge of the clock signal, which is the low to high transition, whereas asynchronous ripple counters count on the falling edge of the clock signal, which is the high to low transition.

- It may appear unusual that ripple counters change state on the falling edge of the clock cycle, but this makes it easier to connect counters because the most significant bit (MSB) of one counter can drive the clock input of the next.

- This works because the next bit must change state when the previous bit goes from high to low – the point at which the next bit must carry. Synchronous counters typically include a carry-out and a carry-in pin for connecting counters without introducing propagation delays.

Advantages of Synchronous Counter

- It is less difficult to design than the Asynchronous counter.

- It works in tandem.

- There is no propagation lag associated with it.

- Because the count sequence is controlled by logic gates, the chances of error are reduced.

- Asynchronous counter operation is faster.

Disadvantages of Synchronous Counter

- This task necessitates a substantial amount of additional logic.

- As the number of states increases, the circuit becomes more complicated.

- All flip-flops in an asynchronous counter are driven by a single, common clock pulse.

- They require more components and hardware than asynchronous counters.

Applications of Synchronous Counter

- Machine Motion Control.

- RPM counter for a motor.

- Rotary Shaft Encoders.

- Digital clock or pulse generator.

- Alarm clocks and digital clocks