Wafer sort (or wafer test) is a part of the testing process performed on silicon wafers. Wafer sort is a simple electrical test that is performed on a silicon die while it’s in a wafer form.

It intends to identify the non-functional dies, thereby avoiding assembly of those dies into packages. Wafer sort is a simple and quick test which basically focuses on a few electrical parameters, especially on the ones that are most likely to fail.

afer testing is performed during IC production on every wafer and even on every silicon die, otherwise, there could be defective semiconductor dies which when go through the assembly process eventually lead to unnecessary expenses at the end of the manufacturing process.

One can spot wafer sort as a financial decision that depends on yield, volume and packaging cost. But in some cases, companies perform wafer sort to monitor the silicon foundry yield. This feedback is then feedbacked to the fab to further optimize the silicon manufacturing process ,thereby improving the process yield.

A digital wafer map is attached to each tested wafer to label the passing and non-passing dies.

Perturbed about the functioning? Here is the answer .

Called by different names such as the Electronic Die Sort (EDS), Circuit Probe (CP), and the Wafer Test (WT). This is the testing performed on the wafer or part of the semiconductor that carries the internal circuitry. Only because the circuitry is small and visual detection of any defects is virtually impossible, the testing however is performed using specific equipment once the creation of wafer has been completed . The wafer testing is done just before it is sent to the die packaging phase. The integrated circuits, found on the wafer are regularly checked for defects. The process uses various test patterns to find defects and eliminates the wafer from the very next step . The testing itself is performed by an ATE that has a wafer prober.

What is a Wafer Prober?

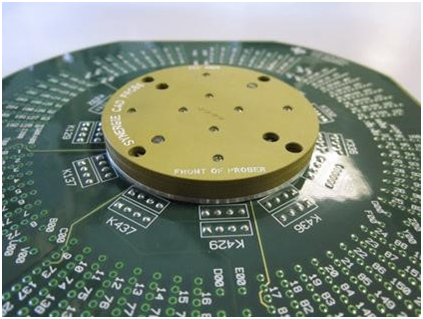

A Wafer prober is a device or machine that carries out the functions of the wafer sort or testing of the integrated circuits. How it works is rather simple. During the testing process, the probe card (which consists of several microscopic contacts) is located inside the wafer prober when the wafer itself is positioned for electrical contact. The wafer is mounted on what is known as a wafer chunk to keep it in a position. The hold is vacuum-sealed (indicating its firmness) but temporary so that another wafer can quickly be moved into the position once the testing is over.

When each die has been tested electronically by the prober, it moves to the next die where another line can be tested. The prober will repetitively load and unload the wafer from the carrying device. In addition, it is equipped with optics for automatic pattern recognition so that the wafer is aligned properly for the testing process. That way the testing can be performed with the utmost accuracy ensuring that a failure is not due to the incorrect alignment of wafer.

The contact pads on the wafer are touched by the tips of the needles from the wafer prober. This allows electricity to be conducted properly (through the wafer) which will successfully complete the test and hence followed by the test of next line or circuit. However, if the electrical test is failed , the wafer is moved from the manufacturing process for separate testing.

The wafer prober can also handle multi-die packages like the System in Package (SiP) or the Stacked Chip-Scale Package (SCSP) , all thanks to the non-contact probes . This allows the proper identification of the Known Tested Die (KTD) as well as the Known Good Die (KGD) which are obviously vital to increase the yield of the overall system .

Uncomplicated Additional Testing

The ATE will test circuitry along the scribe lines. Performance of the device can be rated when using line test structures. Use of such a process makes easier for companies to fetch information. There are some dies that include internal spare resources which are used for repairs, such as the one found on flash memory IC. If some test patterns are not passed, the additional resources available can be used.

The redundant die which has already been failed in certain tests will be discarded . During the testing process, circuits that do not pass electricity must be marked with a small ink dot located in the middle so that wafermap can store the information of failed or inactive circuits.

What is a Wafermap?

A Wafermap is a map that reveals the passing and non-passing dies using bins. The bin itself is defined as either a good or a bad die, depending upon the nature of the die.

The wafermap will be sent electronically to the assembly house that picks up the passing dies by choosing the bin number which only contains good dies .

In the past, the good dies were marked using ink dot(s), but this process is not common anymore. The use of ink dots allows visual inspection because an operator can disqualify a die based on the ink dot(s). Hence, the only die(s) which pass all the test patterns will be used . There are cases in which the even the dies having flaws can be incorporated if their flaws don’t significantly interfere with the device in which it’s placed .

Aftermath of the IC Packaging

The packaged chip will be next tested during the well-known IC phase. This testing process is very similar but not actually identical to the original wafer test approach. While this might be seen by some as redundant but fortunately it does serve any extra step to catch any kind of defect(s) in the assembly process like that of missing bumps or wirebonds.

This double-check helps to keep defective dies from being sold or used in devices that help in creating considerable cost in detecting and replacing. However, there is always some kind of considerable cost in the testing process, so it is not at all surprising that some companies produce a high yield of dies skipping testing altogether and risking blind assembly which eventually leads to greater efficiency.