What is a MOD Counter?

- A Modulus-M Counter is a counter in which M represents the number of states present. M = 2n(2 raised to power n), where ‘n’ is the number of flip-flops required to design the modulus-M counter.

- The modulus-6 counter, for example, has six states. The value of n, in this case, is 3. That means the module-6 counter requires three flip-flops to be designed.

- MOD Counters are cascaded counter circuits that count to a predetermined modulus value before being reset.

- A counter’s job is to count by advancing its contents by one count with each clock pulse. Counters in a “count-up” mode advance their sequence of numbers or states when activated by a clock input. Similarly, counters that reduce their sequence of numbers or states when activated by a clock input are said to be in “count-down” mode. Bidirectional counters are those that can operate in both the UP and DOWN directions.

- Counters are devices that use sequential logic and are activated or triggered by an external timing pulse or clock signal. A counter can be built to work as either a synchronous or asynchronous circuit. When a clock signal is applied to synchronous counters, all of the data bits change synchronously. An asynchronous counter circuit, on the other hand, is independent of the input clock, so the data bits change state one after the other.

- Counters, on the other hand, are sequential logic devices that execute a predetermined sequence of counting states when triggered by an external clock (CLK) signal. The modulus is the number of states or counting sequences through which a specific counter advances before returning to its original first state (MOD). In other words, the modulus (or simply modulo) is the counter’s dividing number and the number of states it counts.

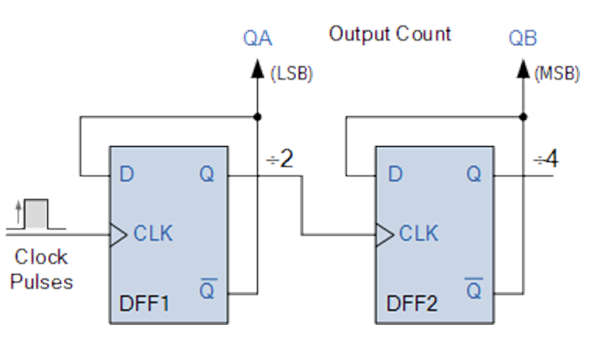

- Modulus Counters, or simply MOD counters, are defined by the number of states they will cycle through before returning to their original value. For instance, consider a 2-bit counter that counts from 00 to 11.

- In binary, that is 0 to 3 in decimal, has a modulus value of 4 (00 1 10 11, and return to 00), and is thus known as a modulo-4, or mod-4, counter. It’s also worth noting that it took four clock pulses to get from 00 to 11.

- Because there are only two bits in this simple example (n = 2), the maximum number of possible output states (maximum modulus) for the counter is:

2n(2 raised to power n) = 2×2 = 4. - Counters, on the other hand, can be designed to count to any number of 2n(2 raised to power n) states in their sequence by cascading multiple counting stages into a single modulus or MOD-N counter.

- As a result, to count a single data bit while providing 2n(2 raised to power n) different output states, a “Mod-N” counter will require “N” flip-flops connected (n is the number of bits). It should be noted that N is always a whole integer value.

Divide-by-two Counter

- In the Sequential Logic D-type Flip-Flops can be connected to form a Data Latch. The D-type Flip-Flop is also be used as a binary divider, for Frequency Division, or as a “divide-by-2” counter.

- As shown below, the inverted output terminal Q (NOT-Q) is connected directly back to the Data input terminal D, providing the device with “feedback.”

- We can’t count unless we have some kind of memory, which may seem obvious. The Divide-by-2 Counter is the first simple counter we can build now that we have memory access via flip-flops.

![]()

- The inverted output Q’ is fed into the D input here. This means that whenever the clock signal has a rising edge, our output will flip states.

![]()

- So there is some disagreement. But how should we interpret this in terms of counting?

- Consider what happens when we assign numbers to voltage levels. 0 equals LOW, 1 equals HIGH. If we interpret the Clock levels as the one’s bit and the Q out as the two’s bit, we get a binary counter that counts from 0 to 3 and then resets.

- As a result, our Divide-by-2 counter enables us to count clock pulses in a meaningful manner. However, we have a severe limit on how high we can count with just one D-flop. If these circuits are to be useful, we must find ways to count beyond four.

Design Mod – N Synchronous Counter

Step 1:

- Decide on the number of flip-flops – For example, if we are designing a mod N counter and n flip-flops are required, we can use this equation to determine n. N <= 2nHere, we are creating a Mod-10 counter. As a result, N= 10 and the number of flip flops(n) required is For n = 3, 10=8, which is false. For n= 4,10=16, this is correct. As a result, the Mod-10 counter requires four FF.

Step 2:

- Create a flip-flop excitation table using T FF.

| Previous state (Qn) | Next State (Qn+1) | T |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Step 3:

- Create a state diagram.

![]()

- A decade counter is also known as a mod -10 or divide by ten counter. It counts from 0 to 9 before returning to 0. It counts in the standard binary sequence. Four T flip-flops are used here. After Q3 Q2 Q1 Q0 = 1001, it resets.

Step 4:

- Create a Karnaugh map in terms of flip-flop outputs as the input variable for each FF input –

![]()

Step 5:

- Draw a circuit diagram – A negative edge-triggered clock is used here for toggling.

- The clock is provided to each Flip flop at the same time.

- According to the simplified K map equation, the toggle(T) input is provided to each Flip flop.

![]()

Timing diagram:

- Toggling is used here.

- Only when an FF’s toggle input (T) is 1, will its state change.

![]()

Explanation:

- Q3 Q2 Q1 Q0 are initially 0 0 0 0.

- The timing diagram can be used to verify the counter sequence. Because T0 is connected to logic 1, Q0 toggles on every falling edge of the clock output.

- T1 becomes 1 only when the expression T1 = Q’3Q0 becomes 1. If the clock falls edge occurs (due to negative edge triggering), the output state of T1, i.e. Q1, changes.

- T2 becomes 1 only when the expression T2 = Q1Q0 becomes 1. If the clock falls, the output state Q2 changes.

- T3 becomes 1 only when the result of the expression T1 = Q3Q0 + Q2Q1Q0 is 1. If the clock falls edge occurs (due to negative edge triggering), the state of Q3 changes.

- We get the following output: Q3(MSB) Q2 Q1 Q0 (LSB).

- After the tenth falling edge, the output state of all FFs returns to 0 0 0 0.