Frequency-Division-Divide-by-2-Counter

- In the Sequential Logic D-type Flip-Flops can be connected to form a Data Latch. The D-type Flip-Flop is also be used as a binary divider, for Frequency Division, or as a “divide-by-2” counter.

- As shown below, the inverted output terminal Q (NOT-Q) is connected directly back to the Data input terminal D, providing the device with “feedback.”

- We can’t count unless we have some kind of memory, which may seem obvious. The Divide-by-2 Counter is the first simple counter we can build now that we have memory access via flip-flops.

![]()

- The inverted output Q’ is fed into the D input here. This means that whenever the clock signal has a rising edge, our output will flip states.

![]()

- So there is some disagreement. But how should we interpret this in terms of counting?

- Consider what happens when we assign numbers to voltage levels. 0 equals LOW, 1 equals HIGH.

![]()

- If we interpret the Clock levels as the one’s bit and the Q out as the two’s bit, we get a binary counter that counts from 0 to 3 and then resets.

![]()

- As a result, our Divide-by-2 counter enables us to count clock pulses in a meaningful manner. However, we have a severe limit on how high we can count with just one D-flop. If these circuits are to be useful, we must find ways to count beyond four.

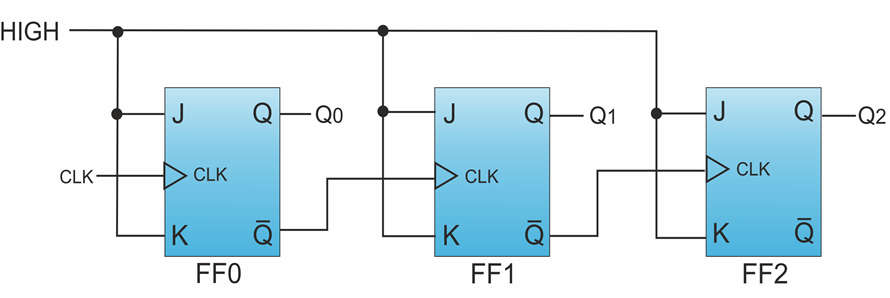

- Chaining Divide-by-2 counters together is a good first idea for making counters that can count higher. The Q from one flop can be fed into the CLK of the next stage. The result looks like this:

- The ripple counter is simple to use. Each stage acts as a Divide-by-2 counter on the signal from the previous stage. The Q signal from each stage serves as both an output bit and a clock signal for the next stage.

![]()

- We can connect as many ripple counters as we want. A three-bit ripple counter counts 23=8 numbers, whereas an n-bit ripple counter counts 2n numbers.

- The issue with ripple counters is that each new stage added to the counter introduces a delay. When we look at a less idealized timing diagram, we can see this propagation delay:

![]()

- As we can see, the propagation delay not only slows down the counter but also introduces errors into the system. As we add more stages to the ripple counter, the errors increase.

The Toggle Flip-Flop

- The toggle flip-flop is another name for the T flip-flop. The JK flip-flop has changed. The T flip flop is obtained by connecting the two inputs of a JK flip flop. By connecting the inputs ‘J’ and ‘K,’ the T flip-flop is received. When T = 0, both AND gates are turned off. As a result, the output remains unchanged. When T equals 1, the output is toggled.

- Toggle flip flops can be constructed using D-type flip flops or standard JK flip flops such as the 74LS73. As a result, the device only has two inputs, the “Toggle” input, and the negative controlling “Clock” input, as shown.

- Whenever two JK flip-flops are required at the same time, the 74LS73 DUAL JK FLIP FLOP IC is the best choice. It has two internal JK flip-flops. Both have distinct structures. They don’t rely on each other or anything else. A single flip-flop could even be used without the other.

![]()

- Binary ripple counters can be constructed by connecting the output of one “Toggle” or “T-type flip-flop” to the clock input of the next. Because toggle flip-flops toggle from one state to the next (HIGH to LOW or LOW to HIGH) at every clock cycle, simple frequency divider and ripple counter circuits can be easily built using standard T-type flip-flop circuits.

- J and K are two additional inputs. The operation is identical to that of SR flip-flops for achieving a toggling function. A HIGH input to RESET will activate it, and low inputs will deactivate it.

![]()

- The Truth Table JK Flip Flop:

| ClK | J | K | Q | Q’ | State |

|---|---|---|---|---|---|

| 1 | 0 | 0 | Q | Q’ | No Change in State |

| 1 | 0 | 1 | 0 | 1 | Resets Q to 0 |

| 1 | 1 | 0 | 1 | 0 | Sets Q to 1 |

| 1 | 1 | 1 | – | – | Toggles |

Working of 74LS73 DUAL JK FLIP-FLOP

- To understand 74LS73, we must first understand the SR latch. There are two inputs in an SR latch. The first is known as a reset and the second is a set. At least one pin on the output should be HIGH, while another should be LOW. When there are different inputs on both input pins but the outputs are the same, the output becomes invalid in the case of 1,1 and the output becomes unpredictable in the case of 1. To address this issue, an internal clock has been installed in the JK flip-flop. The clock regulates the change in output based on the input state.

![]()

- As shown in the image above, the JK flip flop contains two SR latches and four NAND gates. The first latch serves as the Master, while another SR latch serves as the Slave. The input to Master SR Latch is provided by the two NAND gates and Slave SR Latch. The output of the Slave latch to Master aids in the toggle of the JK flip flop. pulse. The NAND Gates are connected to the Master’s input signal. The output of the NAND gates has been connected to another pin known as the clock pin. When the CLOCK pin receives a rising pulse, the NAND gate can only send the output to the master.

- When the clock is LOW, there is no output. In the event of a LOW Pulse, the output will be ignored. When a HIGH to LOW pulse is applied to the Input gate of the Slave Latch, the output of Master Latch is sent to the Slave. The clocking process between the Master and Slave causes the flip flop to transfer data from the Master to the Slave using a timing signal.

- The Toggle or T-type flip-flop is an edge-triggered divide-by-2 device that is triggered on the rising edge of the clock signal and is based on the standard JK-type flip-flop. As a result, each bit moves right by one flip-flop. All of the flip-flops can be reset asynchronously and triggered to turn on either the leading or trailing edge of the input clock signal, making it ideal for Frequency Division.